RISC-Y Business

A 3-stage RISC-V CPU implementing the full RV32I instruction set

Project Overview

RISC-Y Business is a 3-stage pipelined RISC-V CPU that implements the complete RV32I instruction set. This project was designed to explore computer architecture principles and gain hands-on experience with hardware description languages.

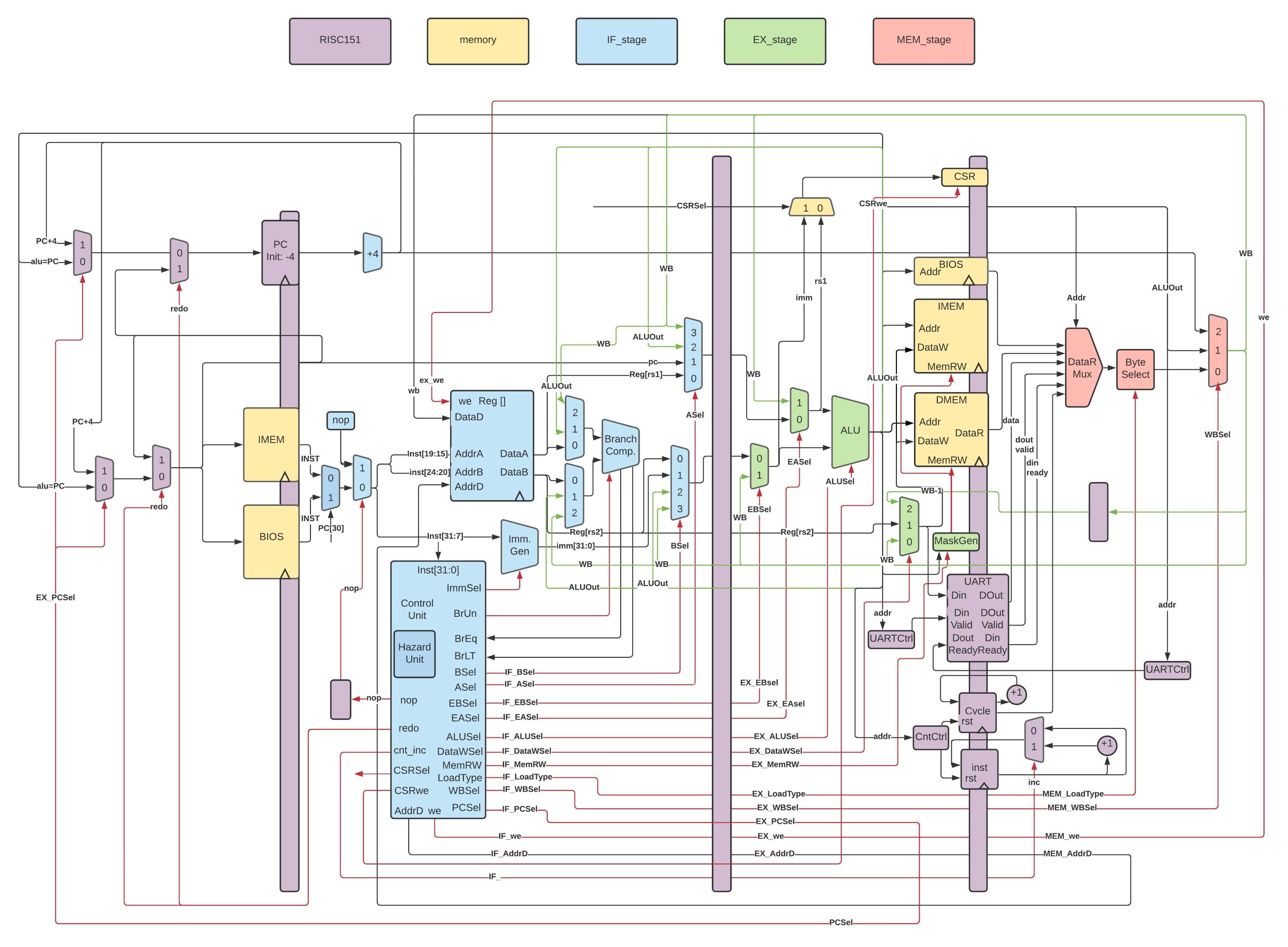

Architecture

The CPU features a classic 3-stage pipeline:

- Fetch (IF_stage): Retrieves instructions from memory

- Decode & Execute (EX_stage): Decodes instructions, reads register values, and performs ALU operations

- Memory & Writeback (MEM_stage): Handles memory access and register writeback

RV32I Instruction Set

The implementation supports all RV32I base integer instructions, including:

- Integer computational instructions

- Control transfer instructions

- Load and store instructions

- Memory ordering instructions

- Environment call and breakpoints

Technical Details

The CPU was implemented in SystemVerilog and tested on an FPGA development board. Key features include:

- 32-bit data path

- 32 general-purpose registers

- Harvard architecture with separate instruction and data memory

- Forwarding logic to minimize pipeline stalls

- Branch prediction for improved performance

Performance

The CPU achieves a clock frequency of 50MHz on the target FPGA, with an average CPI (Cycles Per Instruction) of 1.2 for typical workloads. The implementation prioritizes correctness and readability over maximum performance.

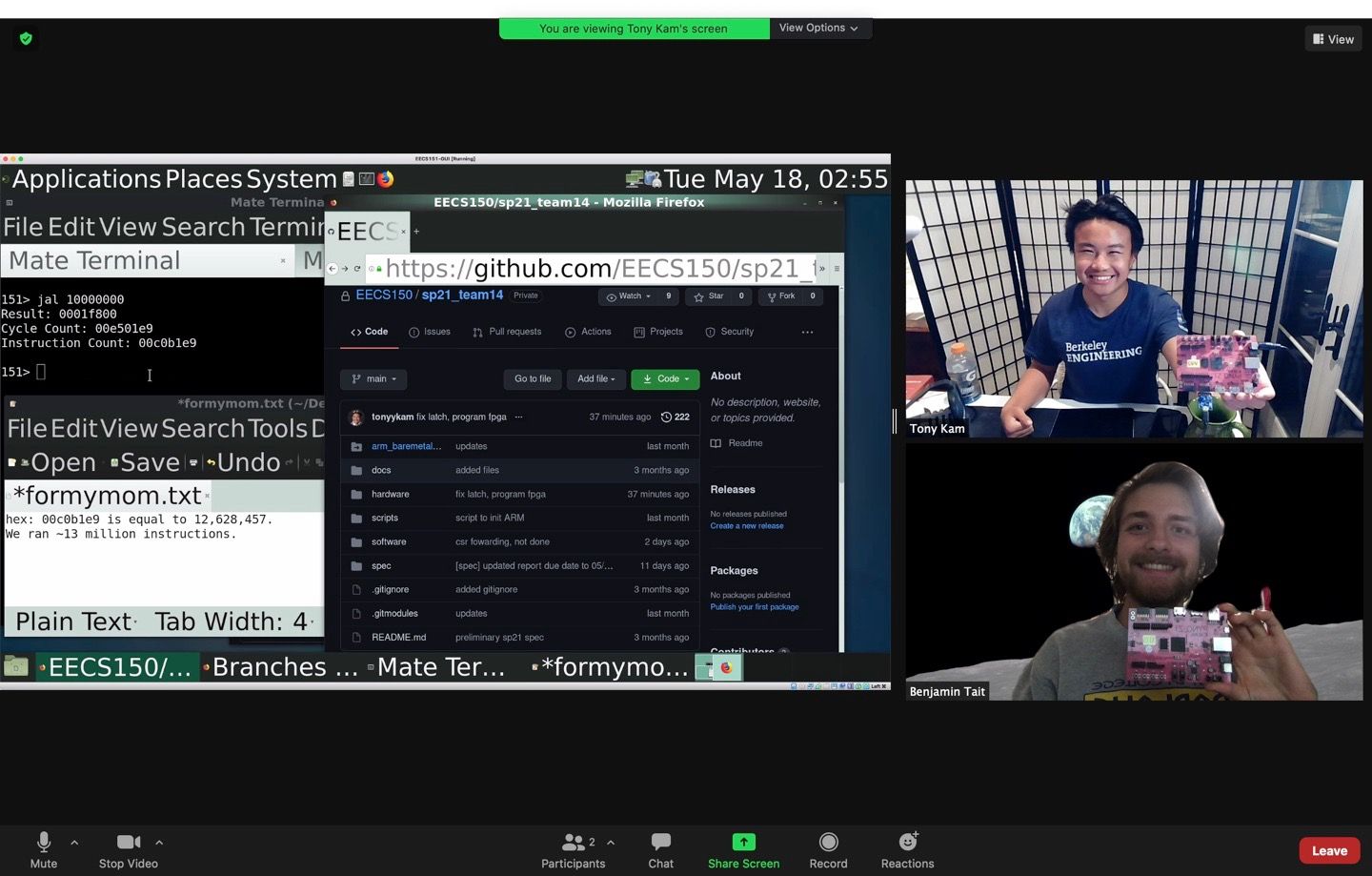

In testing, we successfully ran over 13 million instructions, validating the correctness of our implementation against the RISC-V specification.

Team

This project was developed as part of UC Berkeley's EECS150 (Digital Design and Computer Architecture) course. The implementation was a collaborative effort between Tony Kam and Benjamin Tait, combining expertise in computer architecture, digital design, and hardware description languages.

Future Work

Planned enhancements include:

- Adding support for the RV32M extension (integer multiplication and division)

- Implementing a 5-stage pipeline for improved performance

- Adding a simple cache hierarchy

- Exploring superscalar execution